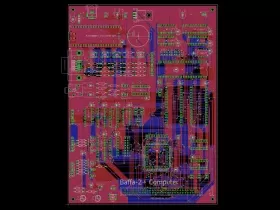

Baffa CP/M Single Board Computer 2

Back to Hardware Specifications Page

Single Board Computers are a simpler way to experience the capabilities of the Baffa-2 Homebrew Computer. They provide the main features of the "Baffa-2 Default Setup"(

Baffa CP/M SBC) and the "Baffa-2 RomWBW Setup"(Baffa-2+ SBC) on a single, ready-to-use board. The Baffa-2+ SBC was created to power the

Baffa-2+ Computer.

Default Features:

- CPU: Z180 running at 18.432 MHz

- Interface: Two high-speed serial ports up to 115200 Baud. Port A attached to video terminal. Port B can be connected to ESP-1 Modem Emulation.

- Disk: SDCard Disk Module.

- RAM: 512KB

- ROM: 512KB RomWBW

- RTC: DS1302 Real Time Clock

- PSG: YM2149 / AY-3-8910

More info about...

Baffa-2+ Single Board Computer Rev.0

Baffa CP/M SBC2

Baffa CP/M SBC2 Rev.0

Related Files:

Firmware:

Bus Expansion Header

| Pin | Signal | Pin | Signal |

|---|

| 1 | A0 | 2 | A1 |

| 3 | A2 | 4 | A3 |

| 5 | A4 | 6 | A5 |

| 7 | A6 | 8 | A7 |

| 9 | A8 | 10 | A9 |

| 11 | A10 | 12 | A11 |

| 13 | A12 | 14 | A13 |

| 15 | A14 | 16 | A15 |

| 17 | A16 | 18 | A17 |

| 19 | !M1 | 20 | A18 |

| 21 | CLK | 22 | !INT |

| 23 | !MREQ | 24 | !WD |

| 25 | !RD | 26 | !IORQ |

| 27 | D0 | 28 | D1 |

| 29 | D2 | 30 | D3 |

| 31 | D4 | 32 | D5 |

| 33 | D6 | 34 | D7 |

| 35 | TX1 | 36 | RX1 |

| 37 | A19 | 38 | !RESET |

| 39 | GND | 40 | VCC |

| 41 | !RFSH | 42 | - |

| 43 | CLK2 | 44 | !BUSACK |

| 45 | !HALT | 46 | !BUSRQ |

| 47 | !WAIT | 48 | !NMI |

| 49 | - | 50 | - |

| 51 | - | 52 | - |

| 53 | - | 54 | - |

| 55 | - | 56 | - |

| 57 | TX2 | 58 | RX2 |

| 59 | !INT1 | 60 | !INT2 |

IOBAR PSG Header

| Pin | Signal | Pin | Signal |

|---|

| 1 | GND | 2 | VCC |

| 3 | IOB7 | 4 | IOB6 |

| 5 | IOB5 | 6 | IOB4 |

| 7 | IOB3 | 8 | IOB2 |

| 9 | IOB1 | 10 | IOB0 |

| 11 | IOA7 | 12 | IOA6 |

| 13 | IOA5 | 14 | IOA4 |

| 15 | IOA3 | 16 | IOA2 |

| 17 | IOA1 | 18 | IOA0 |

CPU Settings

| JP13 |

|---|

| = | Adds VCC to Port A |

| JP14 |

|---|

| = | Adds VCC to Port B |

| JP9 |

|---|

| = | Set DCD0 to low |

| JP10 |

|---|

| = | Connect X2 Clock to CLKA |

| JP11 |

|---|

| = | Connect X2 Clock to CLKB |

| JP15 |

|---|

| = | Connect X2 Clock to CLK2 |

| JP2 |

|---|

| = | Connect TX1 to TXA |

| JP5 |

|---|

| = | Connect RX1 to RXA |

| JP6 |

|---|

| = | Connect TX2 to TXB |

| JP7 |

|---|

| = | Connect RX2 to RXB |

| JP16 |

|---|

| =o | ROM Read-only |

| o= | ROM Write Enabled |

PSG Settings

Default Port Z180: 60h / 68h

| JP19 (Use A4 for Enable JP4) |

|---|

| =o (1-2) | VCC |

| o= (2-3) | A4 |

| JP18 (CS) | VCC | A4 |

|---|

| pin1 |8888888 | 00h | 10h |

| pin2 8|888888 | 80h | 90h |

| pin3 88|88888 | 40h | 50h |

| pin4 888|8888 | C0h | D0h |

| pin5 8888|888 | 20h | 30h |

| pin6 88888|88 | A0h | B0h |

| pin7 888888|8 | 60h | 70h |

| pin8 8888888| | E0h | F0h |

| JP12 (Enable Selector) |

|---|

| =o (1-2) | CS |

| o= (2-3) | A15 |

| JP21 (Reg) |

|---|

| pin1 |88 | A14 |

| pin2 8|8 | A3 |

| pin3 88| | A2 |

| A2 (JP12 CS/A15) | A3 (JP12 CS/A15) | A14 (JP12 CS/A15) | A15 | A14 | WR | RD | - | BDIR | BC1 |

|---|

| 0000h/8000h | 0000h/8000h | 0000h/8000h | 1 | 0 | 0 | 1 | Y4 | 1 | 0 |

| 0004h/8004h | 0008h/8008h | 4000h/C000h | 1 | 1 | 0 | 1 | Y5 | 1 | 1 |

| 0000h/8000h | 0000h/8000h | 0000h/8000h | 1 | 0 | 1 | 0 | Y2 | 0 | 0 |

| 0004h/8004h | 0008h/8008h | 4000h/C000h | 1 | 1 | 1 | 0 | Y3 | 0 | 1 |

| JP20 |

|---|

| = | AY8910 TEST2 |

| = | YM2149 divides the input clock by 2 |

| oo | disabled |

RTC Settings

Default Port RTC DS1312: 0Ch / 0Eh (000011x0)

Terminal Settings

| JP4 - TX Port |

|---|

| =o | Connect Terminal to TXA Port |

| o= | Connect Terminal to TXB Port |

| JP8 - RX Port |

|---|

| =o | Connect Terminal to RXA Port |

| o= | Connect Terminal to RXB Port |

Related Datasheets:

Related Projects:

Related Revisions:

- Dev/2022 Rev.0

* Fix RTC Address IC7 - Changes from 0xC0 to 0x0C

- May/2022 Prototype (Schematics with errors)

Back to Hardware Specifications Page